Pub手册4.6.4,BIST (Built-In Self-Test) 模块是一种可编程的自检引擎,它为应用程序提供了一种测试 DDR PHY 和 I/O 的方法,主要用于高速生产测试。BIST 模块通过 回路回送(loopback)方式来验证 PHY 的发送路径和接收路径的功能。除此之外,还可以选择测试外部内存的功能。

BIST 模块的功能

- PHY 测试:

BIST 通过将数据从 PHY 的发送路径通过回路回送到接收路径,来测试 PHY 的发送和接收功能。通过此方式,不需要外部存储器即可完成测试。 - I/O 测试:

BIST 还可以测试 I/O 的功能,确保数据能够正确地通过 I/O 接口传输。 - 外部内存测试(可选):

如果需要,BIST 还提供了测试外部内存的功能。此时,BIST 会发送常规的写读事务到外部 DRAM,并比较从 DRAM 读取的数据和写入的数据是否一致。

BIST 模块的工作原理

- 回路回送模式(Loopback Mode):

在回路回送模式下,BIST 将数据从 PHY 的发送路径通过 I/O 返回到接收路径。这样,数据就可以在 PHY 内部进行循环回送,进行自检。这种模式不需要外部内存,因此适用于不需要依赖外部存储器的测试场景。 - DRAM 模式(DRAM Mode):

在 DRAM 模式下,BIST 会向 DRAM 发送正常的写读事务,并将读取的数据与预期数据进行比较。该模式适用于测试外部 DRAM 存储器。

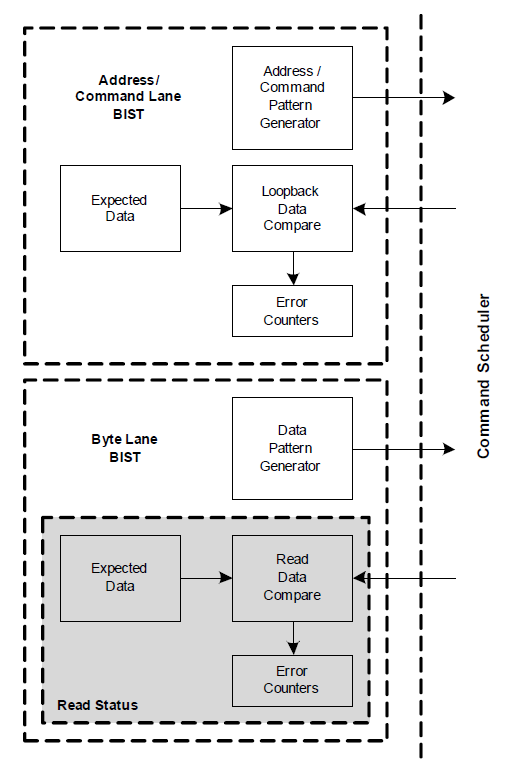

BIST 模块的结构(Block Diagram)

BIST 模块的框图(提供详细图示)展示了各个功能模块之间的连接方式。它通常包括以下几个主要组件:

- 传输路径(Transmit Path):用于将数据从 PHY 的发送端发送出去。

- 接收路径(Receive Path):用于接收回送的数据并进行比较。

- 外部内存接口:如果使用 DRAM 测试模式,则通过外部内存接口与 DRAM 进行通信。

- 测试模式选择器:允许选择回路回送模式或 DRAM 模式。

- 控制寄存器:通过这些寄存器,可以控制 BIST 模块的启停,配置回送模式、DRAM 模式、错误检测等。

通过该图示,用户可以理解如何在不同测试模式下配置 BIST 模块,并进行 PHY 和 I/O 的功能验证。

1. 环回模式(Loopback Mode)

环回模式是用来测试 PHY(物理层)和 I/O 接口的。其原理是将写入的数据直接送回接收路径,这样就不需要外部存储器(例如 DRAM)来进行测试。具体来说:

- DATXn 写路径和接收路径的环回: 在环回模式下,DATXn(数据线组)的写入数据将直接通过 I/O 传输到接收路径上。也就是说,BIST 发送数据之后,数据直接回到发送端,而不经过外部存储器,这样可以用来验证 PHY 数据通道是否正常。

- AC 输出路径的环回: 另外,AC 输出路径也会在 I/O 处被环回到专用的 AC 环回逻辑。AC 是指命令和地址通道(Address/Command),它用于传输内存的读写地址和控制信号。这部分的环回确保地址和命令通道也能正确工作。

这种模式的好处是无需连接外部 DRAM,测试过程可以在没有外部存储器的情况下进行,适合用于检查 PHY 层和 I/O 接口的基本功能。

- 最小的 WL/RL: 环回模式下支持的最小 WL(写延迟)和 RL(读延迟)为 6。WL/RL 是内存操作的延时设置,通常与内存的时序参数有关。BIST 测试时,环回模式对延迟有最低要求。

2. DRAM模式(DRAM Mode)

在 DRAM 模式下,BIST 会像正常的内存访问一样进行读写操作,写入数据到 DRAM 中,并从 DRAM 中读取数据来进行对比。这个模式实际上测试的是内存的数据完整性以及内存与 PHY 接口之间的配合。具体来说:

- 写读事务: 在 DRAM 模式下,BIST 会执行正常的写读事务(Write/Read Transactions)。即,它将数据写入 DRAM 并从 DRAM 中读取数据来进行对比,确保内存和 PHY 层能够正常交互。

- 地址和命令通道的环回: 即使是在 DRAM 模式下,地址/命令通道(Address/Command Channel)依然会在 I/O 处进行环回。这意味着,BIST 不会向外部发送命令和地址信号,而是会将这些信号发送回自身,以确保地址/命令通道的功能正确。

- 外部存储器测试: 在 DRAM 模式下,可以将其用作测试外部内存(例如,外部的 DRAM 存储芯片),通过发送写读事务并进行数据比较,验证 DRAM 和 PHY 层的通信是否正确。

PHY环回功能

PHY(物理层)环回是通过 I/O 接口的环回功能实现的,目的是将从 I/O 驱动出去的数据通过环回机制传回,以便进行测试和验证。环回的实现取决于 PGCR1[IOLB] 寄存器位的设置。

环回机制的工作方式

数据的环回:当数据从 I/O 驱动出来时,它可以在两种不同的位置进行环回:

- I/O的pad侧: 这种方式是将数据在I/O的pad(物理引脚)端进行环回,即数据通过I/O引脚直接返回。

- I/O的核心侧: 另一种方式是在I/O的核心侧进行环回,即数据回到I/O的内部逻辑。

具体选择哪种环回方式,取决于 PGCR1[IOLB] 寄存器位的设置。PGCR1 寄存器中的 [IOLB] 位用于配置环回的模式:

- 如果 IOLB 位设置为某个特定值,它将决定数据是从 pad侧 还是 核心侧 进行环回。

DATX8 Loopback

DATX8 读路径与环回路径:

- DATX8 是 DDR 接口中的一部分,它在数据字节传输中负责读取数据。

- 在环回模式下,DATX8 的读路径会被用作环回路径。也就是说,数据(DQ、DM)和写入的 DQS(数据选通信号)会被环回到 DATX8 读路径中,并被当作 读 DQ/DM 和 读 DQS 来处理。

DQS 信号的对齐问题:

- DQS 是在 DDR 写入操作中与数据一起传输的同步信号。在 写入路径 中,DQS 会相对于 DQ/DM 信号提前 90 度发送,这样可以帮助在读取时对齐数据。

- 但是在 读路径 中,DATX8 期望 读 DQS 和 读 DQ/DM 信号是 边缘对齐(edge-aligned)的,意味着它们应该在时序上保持同步。

问题:

- 在环回测试中,由于 写路径 会将 DQS 信号相对于 DQ/DM 信号提前 90 度(这是为了帮助读取数据),DATX8 读路径会接收到已经提前 90 度的 DQS 信号。这个提前的 90 度是写路径的特性,而 DATX8 需要去掉这个提前,以确保 读 DQS 与 读 DQ/DM 对齐。

解决方案:

- 为了消除这个 90 度的提前,应该通过 设置 LCDL(读取延迟控制)来调整 DQS信号的相位。具体来说:

- 设置 DXnLCDLR4[RDQSD] 和 DXnLCDLR4[RDQSND] 为 0,这样可以去掉读取路径中 DQS 信号的 90 度偏移。

- 这确保了 环回模式 下,DQS 信号相对于 读数据 只会偏移 90 度,且 读取数据 和 读取 DQS 是同步对齐的。

DDR3 写操作的预置(Write Preamble):

- 预置 是指在数据传输开始之前,信号在一定周期内的初始状态。在 DDR3 中,写操作通常有一个 全翻转预置(full toggle preamble),即信号在开始时进行翻转。

- 这个预置是为了保证数据的正确性,确保数据和控制信号能够准确地同步。

环回模式中的问题:

- 在 环回模式 下,数据通过 I/O 路径被送回到接收器。通常在环回测试中,我们期望数据传输的信号在写入路径和读取路径之间能够同步。

- 由于 写预置 是一个全翻转预置,这意味着写入路径中的 DQS(数据选通信号)会进行翻转。

- 但是,如果环回时将这个信号直接送回读取路径,那么读取路径的 DQS 预置 也会跟着翻转,这就与预期的读取数据(通常来自 SDRAM 的数据)不一致。

问题的根源:

- 预期的读取数据 应该是一个稳定的、没有翻转的信号。在标准的 SDRAM 写入操作 中,数据的读取路径中的 DQS 信号应该是一个稳定的 全时钟预置(non-toggling full-clock preamble),而不是像写路径中那样进行翻转。

- 如果将 写预置 在环回模式下直接传递到读取路径,那么读取路径的 DQS 信号也会经历翻转,导致数据和时序的错误。

解决方案:

- 为了保证环回模式下的正确性,需要 生成非翻转的全时钟预置(non-toggling full-clock preamble)信号,而不是全翻转的写预置。通过这种方式,可以确保在环回测试中,DQS 信号与读取数据的同步要求一致,避免了翻转问题。

- 具体来说,环回模式下会 生成与 SDRAM 预期相符的读取数据,即通过 不翻转的时钟预置 来确保 DQS 信号稳定,以匹配标准的 SDRAM 行为。

AC Loopback

1. 地址/命令通道 (AC Lane):

- 地址/命令通道负责与 SDRAM(同步动态随机存取存储器)进行通信,传输地址和控制信号。例如,地址信号 用于定位存储位置,命令信号 用于控制读写操作。

2. AC PHY 环回逻辑:

- 在 DDR3 或 DDR4 系统中,AC PHY 负责处理地址和命令的物理层传输。为了在测试时不依赖外部内存,AC PHY 提供了内建的 环回逻辑,允许将地址和命令信号从 SDRAM 发送到 AC PHY,再从 AC PHY 环回到接收路径。环回后的信号被当作 读取数据 和 读取时钟 进行处理。

3. CK/CK# 时钟信号的环回:

- CK/CK# 是用于同步数据传输的差分时钟信号。在 AC 环回模式下,CK/CK# 信号被环回到 AC PHY,并被当作 读取时钟 来使用。

- 在环回过程中,时钟会被 反向(inverted),以确保 ck_do(环回后的时钟信号)能在 DDR 时钟 的一个周期之前传输,确保第一个环回数据能够被正确地采样。

4. BISTRR[BCKSEL] 寄存器:

- 该寄存器字段用于选择哪个时钟信号(**CK[n]**)将用于捕捉地址和命令信号。在环回模式下,可以根据需要配置时钟源。

5. 时钟反转(Inverted Clock):

- 在 AC 环回模式中,时钟信号会被 反转,这样可以使环回数据在 DDR 时钟周期的 提前一个周期(一个 DDR 时钟周期提前)时被正确采样。

- 反向时钟 的目的是确保 第一个环回的数据 能够在正确的时钟边沿上被采样,从而避免时序问题。

6. cke 和 cs_n 对齐:

- cke(时钟启用信号)和 cs_n(芯片选择信号)会与 ck_do 上升沿对齐。尽管时钟反转了,但因为 cke 和 cs_n 并没有被用于外部 DRAM 的操作,因此在环回测试中它们的对齐不会造成问题。

- 这意味着,即使时钟信号发生了反转,cke 和 cs_n 信号与时钟的对齐状态并不影响环回模式中的测试,因为它们并不直接影响 DRAM 的操作。

环回模式中的信号流程:

- 地址和命令信号:从 SDRAM 发出,通过 AC PHY 环回逻辑,进入 AC PHY 接收路径,并被视为 读取数据。

- 时钟信号(CK/CK#):时钟信号同样被环回,反转后成为用于 读取数据 的时钟信号。

- cke 和 cs_n:这些信号与时钟信号对齐,但由于它们不影响 DRAM,时序对齐不影响测试。

Loopback Data Capture

时钟路径和数据路径的延迟差异

在 环回数据捕获(loopback data capture)模式下,时钟路径和数据路径的延迟存在差异:

- 时钟路径:时钟信号的传播通常会有更大的延迟,因为时钟信号需要经过更多的逻辑单元(如时钟缓冲器、分配网络等)。

- 数据路径:数据从发送端到接收端的路径可能涉及不同的逻辑单元,但相对于时钟路径的延迟,数据路径的延迟通常较小。

这种延迟差异的产生是因为:

- 时钟信号必须被精确同步并分配到所有相关的接收器。

- 数据路径通常依赖于更少的逻辑单元来传输实际的数据。

2. 如何补偿时钟路径和数据路径之间的延迟差异

为了确保 环回数据 的正确捕获,需要补偿时钟路径和数据路径之间的延迟差异。这个补偿的方式是通过增加 数据路径的延迟 来实现,使其与时钟路径的延迟差异相匹配。

- 为了补偿这种延迟差异,可以通过设置 AC BDLs(Address/Command Bus Delay Line)为 0xA 来添加延迟。BDLs 控制 数据路径的延迟,通过设置这些寄存器的值为 0xA,可以在数据路径中引入适当的延迟,使其与时钟路径的延迟差异相匹配。

- AC BDLs: 这是一个控制地址和命令通道中数据路径延迟的寄存器字段。

- 值 0xA:这个值表示一个特定的延迟量,根据设计的要求,这个延迟可以通过该设置来调整。

3. 延迟的计算

补偿的延迟必须满足以下条件:

- 数据路径的延迟必须大于时钟路径和数据路径延迟差异加上捕获触发器的保持时间(Capture FF hold)。

- 这种延迟补偿需要适应不同的 PVT(Process, Voltage, Temperature)角度,即考虑到工艺、工作电压和温度的变化。

换句话说,设置的数据路径延迟应该足够大,以确保数据能够正确捕获,避免因为时钟和数据路径的不同步导致的错误。

4. RTL仿真中的特别情况

在 RTL仿真

中,由于仿真模型通常不考虑时钟和数据路径之间的实际延迟差异,因此不需要显式地为数据路径添加额外的延迟。

- RTL仿真:这是指在设计阶段使用 寄存器传输级(RTL)模型 进行的仿真。在这种仿真中,设计的时钟和数据路径延迟差异通常是通过仿真工具的建模来忽略的,因此无需手动增加额外的延迟。

NOTE

1. AC I/O 接收器默认关闭

- AC I/O 接收器:在 AC(地址/命令)通道中,接收器用于接收来自外部的地址和命令信号(例如,SDRAM 地址、命令信号)。这些接收器通常在系统初始化时处于关闭状态,以节省功耗。

- 必须启用接收器:在进行 AC 环回测试 时,必须确保接收器已被启用,否则环回信号将无法被正确接收。因此,需要通过配置 ACIOCR0[PDR] 寄存器 来启用 AC I/O 接收器。

ACIOCR0[PDR]:这是一个配置寄存器,用于控制 AC I/O 接收器的电源管理。通过设置该寄存器,可以启用这些接收器。

2. DATX8 环回测试前的准备

DATX8:指的是数据通道中的接收器和相关的时序控制信号(如 DQ、DQS 等)。在进行 DATX8 环回测试 时,必须确保与数据通道相关的所有 I/O 接收器和终端电路已启用,且拉电阻(pull-down/pull-up)已配置正确。

启用 DATX8 接收器和终端:通过配置 DXnGCR3 寄存器 来启用接收器、终端(termination)和数据选通信号(DQS)的拉电阻。具体来说:

- 接收器(Receivers):确保接收器能够接收环回信号。

- 终端(Termination):确保数据总线上的信号被适当终结,以避免信号反射。

- DQS 拉电阻(DQS Pulldown / DQSN Pullup):拉电阻用于控制 DQS(数据选通信号)和 DQSN(反向数据选通信号)的电平,以确保信号稳定,避免不期望的浮动电平。

这些配置项都需要在 DATX8 环回测试 前进行编程。

3. 环回测试的步骤总结

- AC 环回测试前:

- 启用 AC I/O 接收器,通过配置 ACIOCR0[PDR] 寄存器。

- DATX8 环回测试前:

- 启用 DATX8 接收器、终端和拉电阻,通过配置 DXnGCR3 寄存器。

这些配置步骤保证了 环回测试 能够成功地进行,确保 地址、命令 和 数据 信号都能够正确地回到接收路径并被正确处理。

4. 寄存器功能概述

- ACIOCR0[*PDR] 寄存器:用于控制 AC I/O 接收器的电源,确保其在进行 AC 环回测试时已经启用。

- DXnGCR3 寄存器:用于配置 DATX8 接收器、终端 和 拉电阻,这些设置是进行 DATX8 环回测试的必要步骤。

本文链接: https://talent-tudou.github.io/2024/11/05/DDR/PUB Architecture-BIST Loopback/

版权声明: 本作品采用 CC BY-NC-SA 4.0 进行许可。转载请注明出处!